High-Performance Communications

Platform

The NMS Communications TX3220 and TX3220C,

members of the TX™ Series, provide powerful and

flexible hardware for a variety of Signaling System

#7 (SS7) applications. SS7, also known as C7, is the

carrier signaling protocol used for call control and

provides Intelligent Networking (IN) and Advanced

IN (AIN) services. SS7 is also often used as the signaling

protocol for voice over Internet Protocol (VoIP) gateway

applications, wireless infrastructure, and for a wide

variety of Enhanced Services, including voice and

fax messaging, one-number/follow-me, and pre-paid

services. A comprehensive SS7

signaling stack which is optimized for the TX

Series is available from NMS Communications.

Features

- Complete SS7 protocol stack support

(MTP, ISUP, TUP, SCCP, TCAP)

- On-board Motorola 68060 processor,

with four additional adjunct 68360 communications

processors, to support up to 16 SS7 channels

- H.100/H.110 (CT Bus)-compliant interfaces

for ease of integration with other technologies,

including allowing interoperability of data communications

and voice streams over the same physical link

- Downloadable control software, minimizing

host overhead and maximizing host processing time

when running applications

- Selection of optional network interfaces

including dual T1 or E1 digital interfaces (configured

on the hardware) or a quad V.35 interface

- 10/100Base-T Ethernet interface to

support the sharing of a single point code by two

separate boards

Configuration

TX3220 Series products are available

in PCI and CompactPCI form factors. The TX3220 and

TX3220C can run the entire NMS SS7 protocol stack

(MTP, ISUP, TUP, SCCP, and TCAP) on-board to both

minimize host loading and increase system scalability.

Each product requires the appropriate SS7 software

runtime license and comes with drivers to support

Windows or Solaris operating systems.

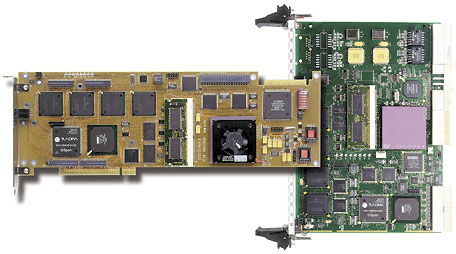

PCI Hardware

The TX3220, a PCI long form factor product,

requires a single PCI slot. The TX3220 includes an

industry-standard H.100 interface for connecting H.100

bus timeslots both to SS7 signaling resources and

to external interfaces supported by the particular

product configuration.

CompactPCI Hardware

The TX3220C, NMS' CompactPCI SS7 product,

requires a single slot in a CompactPCI H.110 chassis.

The TX3220C features an H.110-compliant interface

in an industry-standard CompactPCI form factor. It

offers a higher degree of availability to host systems

by taking advantage of full hot swap support for system

reliability.

Technical Descriptions:

On-board Resources Reduce Host

Overhead

The TX3220 and TX3220C system architectures

are based on a Motorola 68060 microprocessor. Both

architectures couple the 68060 core with four 68360

Quad Integrated Communication Controllers (QUICC).

The combination of the QUICC's intelligent RISC-based

communications engine and the MC68060 CPU processing

power makes the TX SS7 platforms an ideal solution

for demanding communications applications. These platforms

provide high throughput, freeing the host computer

to process user applications.

Multiple Network Interfaces

The TX3220 platform is factory-configured

using interchangeable daughterboards to support a

variety of network interfaces. A single platform can

support either a dual T1, dual E1, or quad V.35 interface.

The TX3220 can support a 10/100Base-T Ethernet interface.

The TX3220C platform comes with rear-mounted

transition cards providing a 10/100Base-T Ethernet

interface. The TX3220C platform can also be factory-configured

using transition cards to support additional dual

T1, dual E1, or quad V.35 interfaces.

The Ethernet interface is required when

deploying two NMS SS7 TX Series platforms in a redundant

configuration. The interface supports a dedicated

point-to-point link to provide extremely fast data

transfer between two TX Series platforms. This approach

avoids the need to transfer MTP-level data over the

host computer's bus and significantly improves SS7

signaling performance.

For the network interfaces, all channels

from the primary rate digital trunk interfaces can

either be terminated locally on the TX product or

switched onto the H.100/H.110 bus for processing by

other H.100/H.110-compliant products.

H.100/H/110 Support Ensures Open

Architecture, Vendor Independence

Support for the H.100/H.110 (CT Bus)

specification is a core element of the TX3220/ TX3220C

architecture. The H.100/H.110 specification gives

developers the flexibility, openness, and vendor independence

to easily deliver the most cost-effective solution.

H.100/H.110 switching on these platforms gives systems

integrators access to other outside resources such

as voice and call processing, modem pools, and speech

recognizers. The H.100/H.110 bus is the basic building

block for creating highly functional, integrated solutions.

The TX3220 provides full support for

the H.100 specification, while the TX3220C offers

full support for the H.110 specification, the CompactPCI

counterpart to H.100. The TX3220C allows hot swapping

of hardware so that host systems need not be powered

down for preventative maintenance or service

Technical Specifications:

General

- Board configurations: 10/100 Base-T

Ethernet interface and choice of one:

- Dual T1 (1.544 Mbps) digital trunk

interface

- Dual E1 (2.048 Mbps) digital trunk

interface

- Quad-port V.35 serial with external

connector pod

- SS7 links: 4 or 16 (T1 or E1) per

board

- TDM bus: One complete H.100/H.110

interface

Software Driver

Support

- Windows® NT 4

- WIndows 2000

- Intel® Solaris™ 8

- SPARC® Solaris 8 (32-bit)

Host Interface

- Electrical: PCI bus Rev. 2.2

- PCI mechanical: PCI bus Rev. 2.1,

long form factor

- CompactPCI mechanical: PICMG 2.0,

Rev 2.1, CompactPCI

- Bus speed: DC to 33 MHz

DSX-1 Telephony

Interface

- Interface: Complete interface to

two T1 trunks (ANSI T1.102, T1.403)

- Framing: D4, ESF

- Insertion/generation and extraction/detection:

ABCD bits

- Line code: AMI, B8ZS

- Zero bits: Selectable B8ZS, jammed

bit (ZCS) or no zero code suppression

- Alarm signal capabilities: Loss of

Signaling Multiframe Alignment and Loss of CRC Multiframe

Alignment (red), Remote Alarm and Remote Multiframe

Alarm (yellow), Alarm Indication Signal (AIS) (blue)

- Counts: Bipolar violation, F(t) error,

and CRC error

- Robbed bit: Selectable on a per-trunk

basis

- Loopback: Per-channel and overall

under software control. Automatic remote loopback

with CSU option

- Connector: Two RJ-48C connectors

CEPT E1 G.703/G.704 Telephony Interface

- Interface: Full featured G.703 2048

kbps trunk interface

- Framing: CEPT G.704

- Insertion/generation and extraction/detection:

ABCD bits for channel associated signaling and HDLC/LAPD

for generating/terminating a data link

- Line code: HDB3 or AMI (in zero code

suppression)

- Zero bits: Selectable B8ZS, jammed

bit (ZCS) or no zero code suppression

- Alarm signal capabilities: Loss of

Frame Alignment (OOF), Loss of Signaling Multiframe

Alignment and Loss of CRC Multiframe Alignment (red),

Remote Alarm and Remote Multiframe Alarm (yellow),

Alarm Indication Signal (AIS) (blue)

- Counts: Bit error rate, CRC errors,

slips, line code violations, far-end block errors

- Loopback: Per-channel and across

channels under software control

- Connector: Two 120-ohm RJ-48C connectors

On-board Processors

and Memory

- Main processor: 66 MHz Motorola 68060

- Communications processors: Four 33

MHz 68360 QUICCs for a total of 16 serial controller

channels

- Memory: 32 MB SDRAM

- ASIC: Lucent Microelectronics Ambassador™

chip family

H.100/H.110

Support

- Flexible connectivity between T1/E1

trunks, 68360s, and H.100/H.110 bus

- 128 full-duplex connections to bus

- 1,024 local connections

- Switchable access to any of 4,096

bi-directional timeslots for up to 2,048 full-duplex

calls

- Individual data lines may be programmed

in groups of four to operate at 2, 4, or 8 Mbps

for direct connection to boards with previous compatible

technology

- Uses Lucent Microelectronics Ambassador

chip family

Standards

- PCI SIG: PCI Specification Revision

2.1

- ECTF: H.100 Revision 1.0; H.110 Revision

1.0

- CompactPCI: PICMG 2.0, Rev 2.1

- Hot Swap: PICMG 2.1, Rev 1.0

- Boards with T1 Interfaces:

- Digital multiplexer requirements

and objectives: AT&T Pub. 43802, July 82

- Service description and interface

specifications: AT&T TR 62411, ACCUNET T1.5

- Carrier to customer installation

DS1 metallic interface: ANSI T1E1/88-001R1,

February 88

- ANSI T1 Standard for ISDN Primary

Rate Interface: T1E1.4/8868 (proposed text)

April 88

- Primary Rate User-network Interface

Layer 1 Specification: ITU-T I.431, June 88

- Boards with E1 Interfaces:

- G.703: Physical/electrical characteristics

of hierarchical digital network

- G.704: Synchronous frame structures

used at primary and secondary hierarchical levels

- G.706: Frame alignment and cyclic

redundancy check procedures

- G.732: Characteristics of primary

PCM multiplex equipment

- G.823: Control of jitter and

wander within digital networks based on 2,048

kbps hierarchy

- ETSI: ETS 300-418, 300-246, 300-247,

300-248

- Primary Rate User-network Interface

Layer 1 Specification: ITU-T I.431, June 88

Power Requirements

- TX3220: 4 A/board @ 5 V0.25 A/board

@ 12 V

- TX3220C: 2 A/board @ 3.3 V2.5 A/board

@ 5 V0.25 A/board @ 12 V

Environment

- Operating Temperature: 0 ºC

to +50 ºC

- Storage Temperature: -20 ºC

to +70 ºC

- Relative Humidity: 5% to 80%, non-condensing

|